A Comprehensive Analysis of 32nmtechnology of Ladner Fischer Adder usingCMOSLogic,PTL,andDPTLFocusing onPower

Keywords:

Large-scaleintegration, LadnerFischeradder, parallelprefixadderComplementaryMetalOxideSemiconductor, PassTransistorLogic, Double PassTransistorLogicAbstract

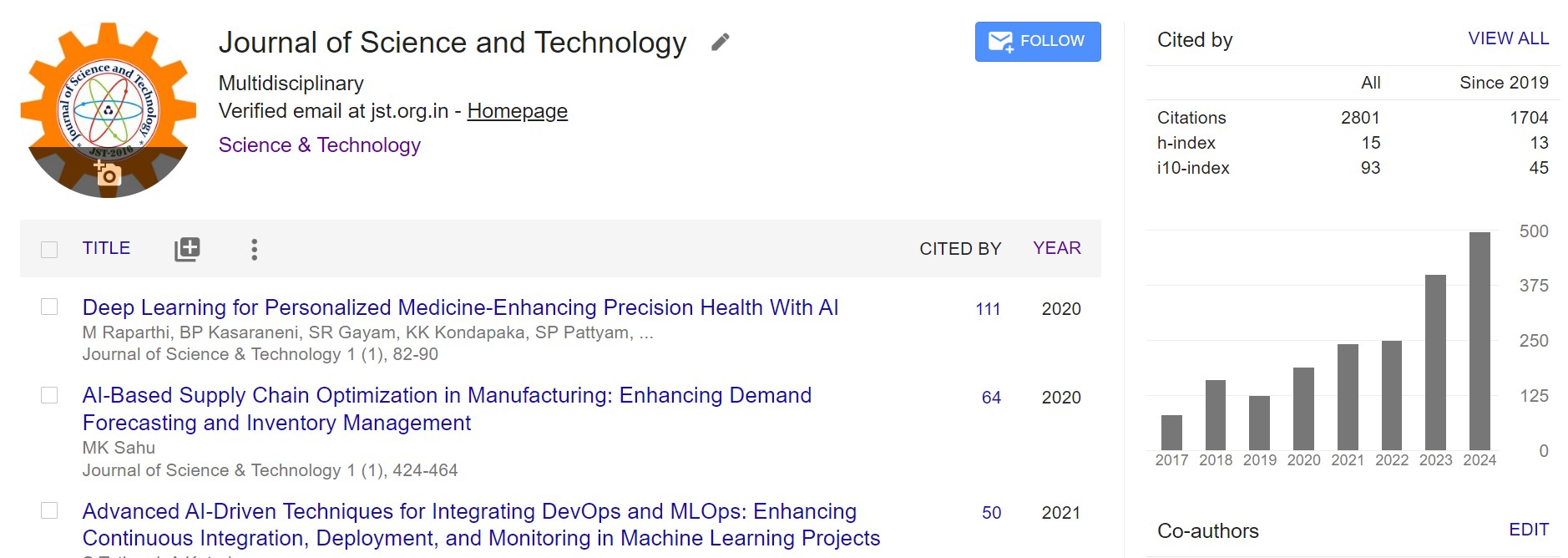

Adders are designed as essential components in digital signal processing and VLSI technologies. Among them, parallel prefixaddersoffersignificantspeedadvantagesovertraditionalbinaryaddersforvariouselectronicapplications.Thispaperexploresthedesignofa4-bitLadnerFischerAdderusingdifferenttechnologieslikeCMOS,PassTransistorLogic,andDoublePassTransistorLogic to achieve a more efficient use of low power. These implementation results demonstrate that the Ladner Fischer adderdesigned with CMOS, PTL, and DPTL has reduced power consumption The simulation was performed using Dsch3 and microwind 3.1tool.