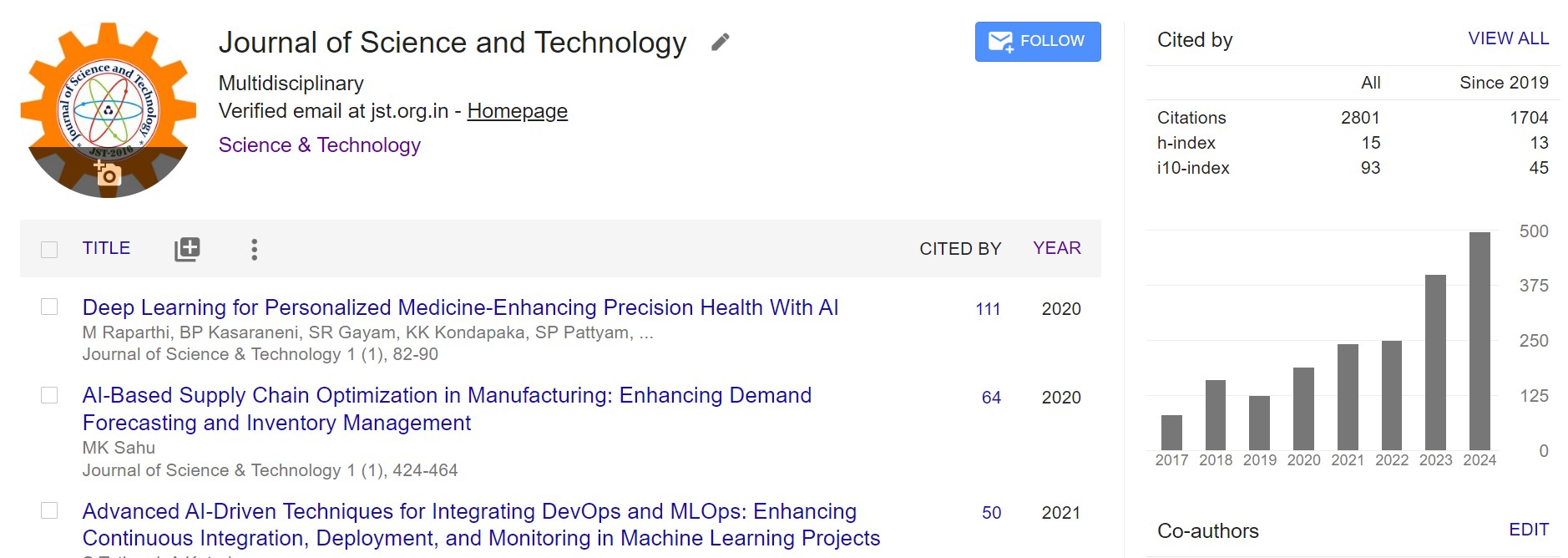

DESIGN AND ANALYSIS OF 32 – BIT HIGH SPEED RISC PROCESSOR USING PIPELINING TECHNIQUE

DOI:

https://doi.org/10.46243/jst.2025.v10.i04.pp34-44Keywords:

RISC, 32-bit processor, pipelining, arithmetic-logic unit (ALU),, Verilog, Xilinx VivadoAbstract

The Reduced Instruction Set Computer (RISC) architecture prioritizes a compact, efficient set of

instructions that execute in uniform cycles, enabling high-performance computing across devices—from

embedded systems to supercomputers. This research presents the design and implementation of a 32-bit

RISC processor leveraging a pipelining technique to enhance throughput while maintaining

computational efficiency. The proposed processor supports 16 arithmetic and logical operations and

adheres to the Harvard architecture, featuring separate data and instruction memories for concurrent access.

The processor incorporates a 32-bit ALU for arithmetic and logical computations, along

with general-purpose registers and a dedicated flag register to track carry, zero, and

parity statuses. The pipelined design divides instruction execution into multiple stages

(fetch, decode, execute, memory access, and write-back), significantly improving

instruction throughput. Each instruction is encoded uniformly, and the design supports

multiple addressing modes for flexibility.