A Novel Reduced Switch Multilevel Inverter Using FPGA

Keywords:

Multilevel inverter (MLI), Field Programmable Gate Array (FPGA) & DriverAbstract

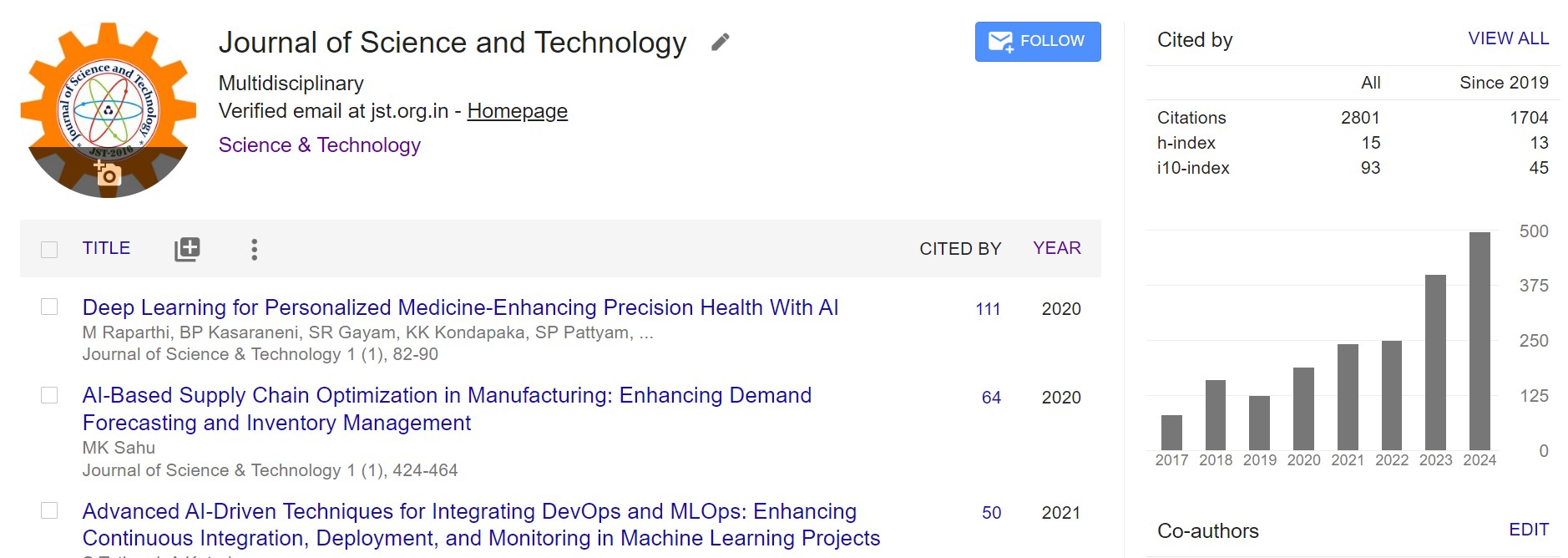

Multilevel inverters (MLI) are mostly used medium-voltage and high-power applications due to its attractive features. As the number of output voltage levels increases, the quality of the output voltage is improved leading to reduction of the filtering requirements. But multilevel inverter requires more number of power semiconductor switches as number of levels increase that increases cost and complexity in control circuit. In this paper, an innovative topology for multilevel inverter is proposed which reduces the number of switches considerably without increasing the total standing voltage of the switches. The proposed topology is a general topology which can be extended for any number of voltage levels. This topology as reduced switch multilevel inverter, we implement and generate the PWM by FPGA Spartron3E processor using VHDL language.