TWO-STEP TDC CMOS RESOLUTION WITH BUILT-IN COARSE GAIN CALIBRATION BY PULSE-SHRINKING FINE STAGE

DOI:

https://doi.org/10.46243/jst.2021.v6.i01.pp185-194Keywords:

.Abstract

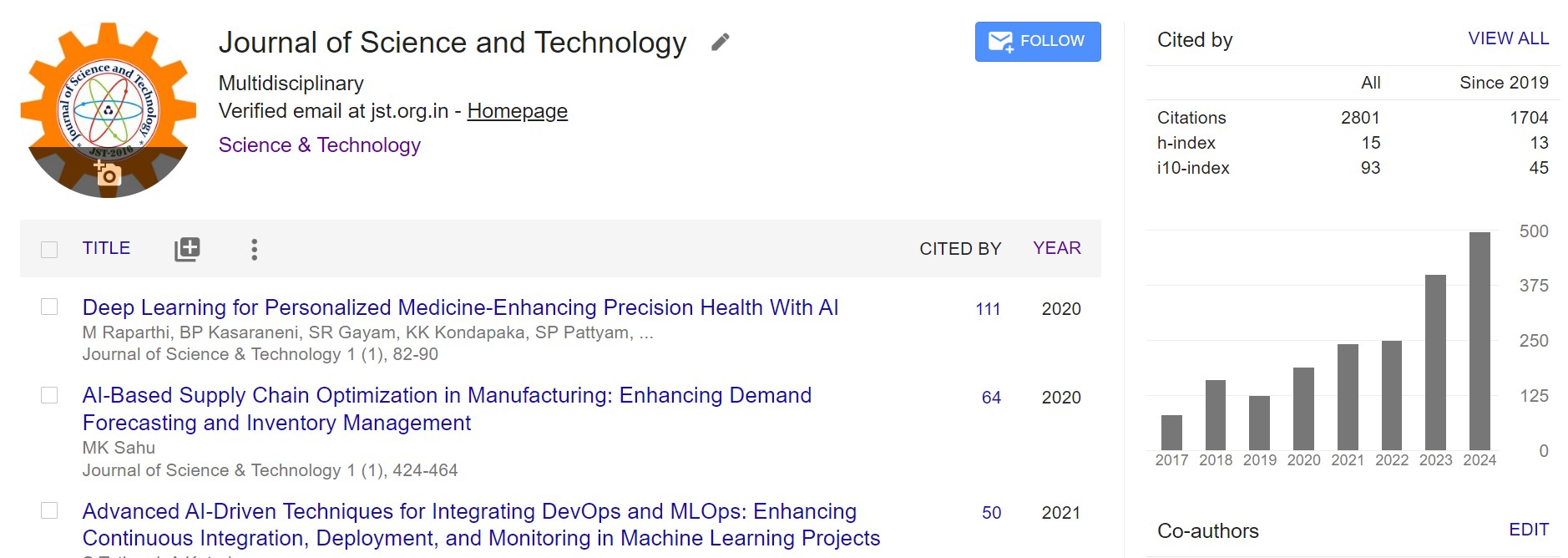

This article proposes a computerized converter (TDC) solution that can meet a broad range of knowledge and fine-time goals at the same time. The proposed TDC utilizes a beat contracting (PS) plot for a precise target and two-advance (TS) engineering for a larger range in the second phase. The suggested PS TDC solves the undesired non-uniform contracting rate issue that plagues conventional PS TDCs by using an assumed counterbalance beat and a balance beat width detecting method. Due to sign spread and extension fraud between coarse and fine phases, the proposed TS architecture achieves nonlinearity with a few methods, resulting in an inferred coarse increase adjustment mechanism. The replication findings in a 0.18-m normal CMOS innovation show 2.0-ps targets and 16-piece go connected to 130-ns input time interim of 0.08-mm2 area in a TDC modification. With an 18.0 maws 1.8-V supply, it has a single-shot accuracy of 1.44 ps and operates at 3.3 MS/