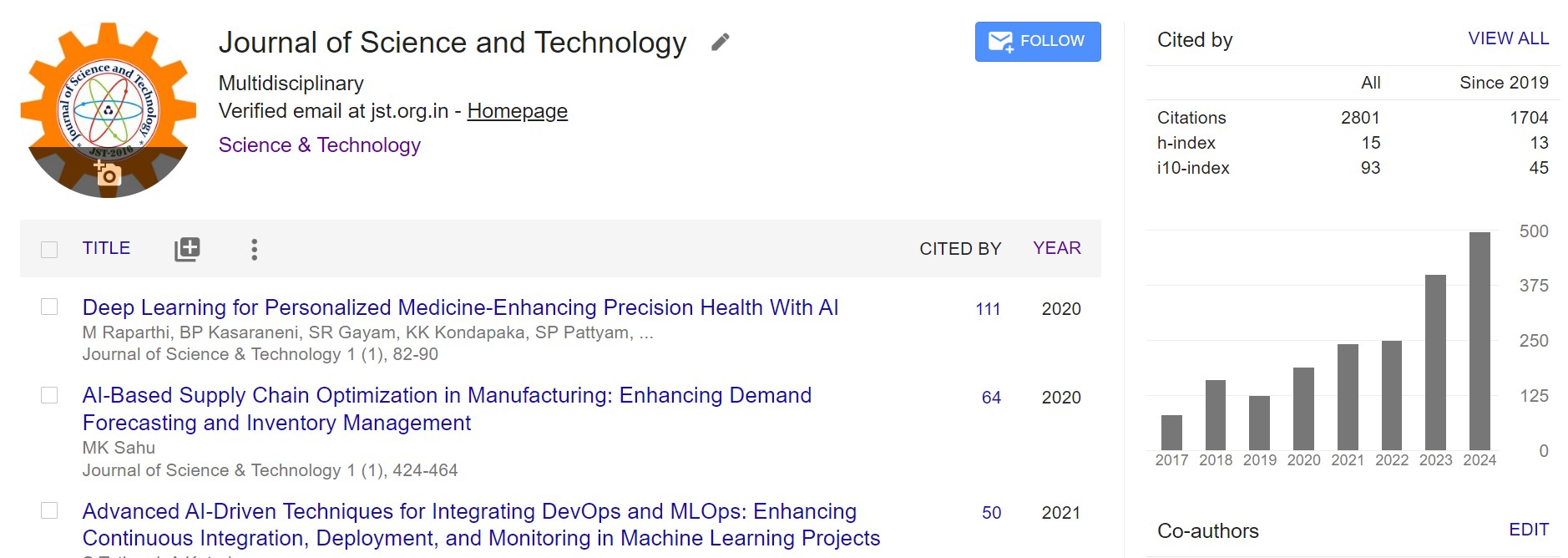

DESIGN AND IMPLEMENTATION OF BUCK CONVERTER TO POWER HIGH SPEED PROCESSOR

DOI:

https://doi.org/10.46243/jst.2022.v7.i03.pp16-21Keywords:

DCDC, PMOS, NMOS, voltage, Cadence toolAbstract

With technological change, there is an additional scope for power management chip. Because of this there is an Erge need for buck converter. In this proposed paper the DC-DC converter is designed for 0.9v. The launch was done using a cadence tool with 90nm technology. Switches used by PMOS and NMOS design of the proposed system. The setting voltage given to the circuit is 1.8v and the output must be 0.9v. The down-to-earth converter is mainly designed for the provision of low power, personal computers, communications and medical electronics in the electronics industry. The input supply will vary and the output will be a DC controlled power supply.