Implementation of Transient Current Testing for Faults in SRAM

DOI:

https://doi.org/10.46243/jst.2020.v5.i6.pp159-164Keywords:

.Abstract

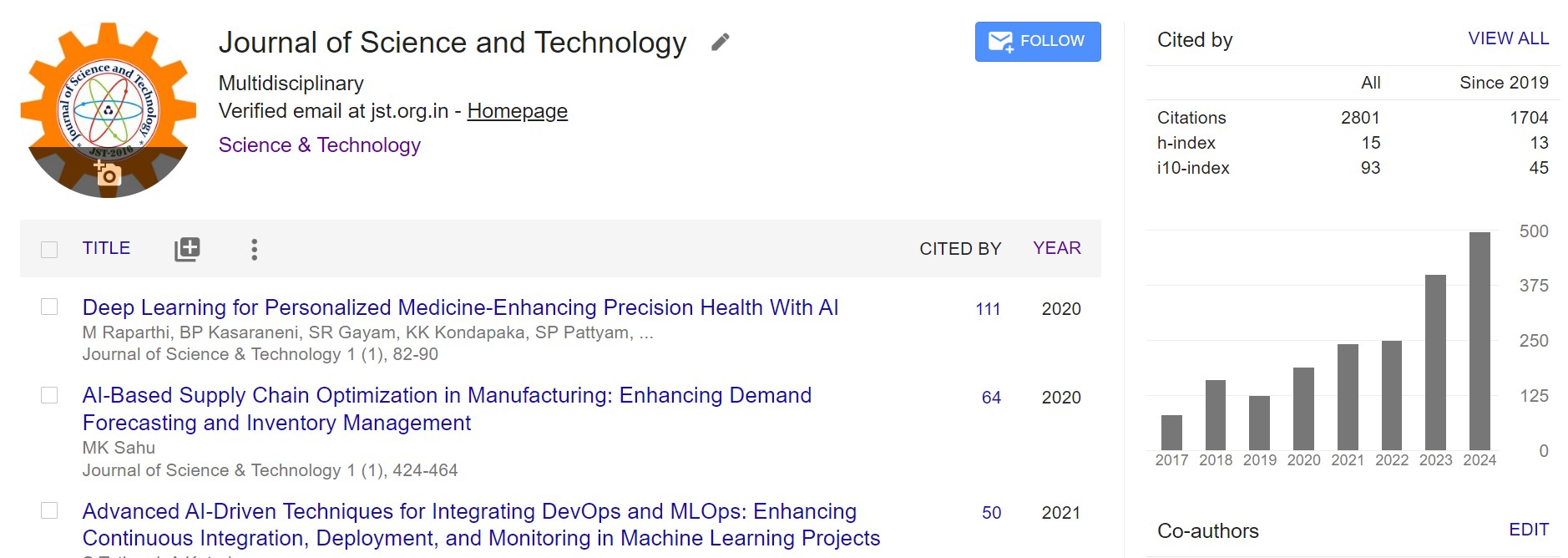

In recent years, as memory devices have risen in popularity, a higher quantity of memory has been packed into each chip, and fierce market competition has upped the quality standards that are expected of the memories that are produced. The notion that failure analysis and device testing methodologies are becoming increasingly important as a result of the rising demand for dependability has been emphasised repeatedly. It has been more popular to study and research memory devices in recent years, particularly in the context of novel failure models, fault detection methodologies, and new memory architectures that have all been developed and implemented. A direct effect of this experience is that the March test is now frequently used to identify and avoid similar problems from occurring in the future. The organisation believes that some vulnerabilities in SRAM cells may go undetected during the normal March testing. In order to determine whether or not there are defects in the CMOS SRAM, a time-consuming procedure has been implemented. It is as a result of this decision that the most recent testing process is selected for usage. As part of this research effort, IDDT is being used to test for faults and issues in CMOS SRAM cells, and it is also being used to test for flaws and issues in CMOS SRAM cells as part of a separate study of the same name. In either case, a transient current pulse generated during a transition write operation or a transition read operation may be monitored for system failures, allowing them to be discovered and remedied. For the purpose of detecting and measuring the transient current pulse, it is required to design a circuit for monitoring current. SRAM, memory testing, the March algorithm, the IDDT, and the current sensor circuit are just a few of the terms that appear in this document.