Performance Evaluation of Approximate (8; 2) Compressor for Multipliers in Error-Resilient Image Processing Applications

DOI:

https://doi.org/10.46243/jst.2024.v9.i4.pp103-112Keywords:

Approximate computing, (8; 2) compressor, multipliers, error-resilient applications, image processing, performance evaluationAbstract

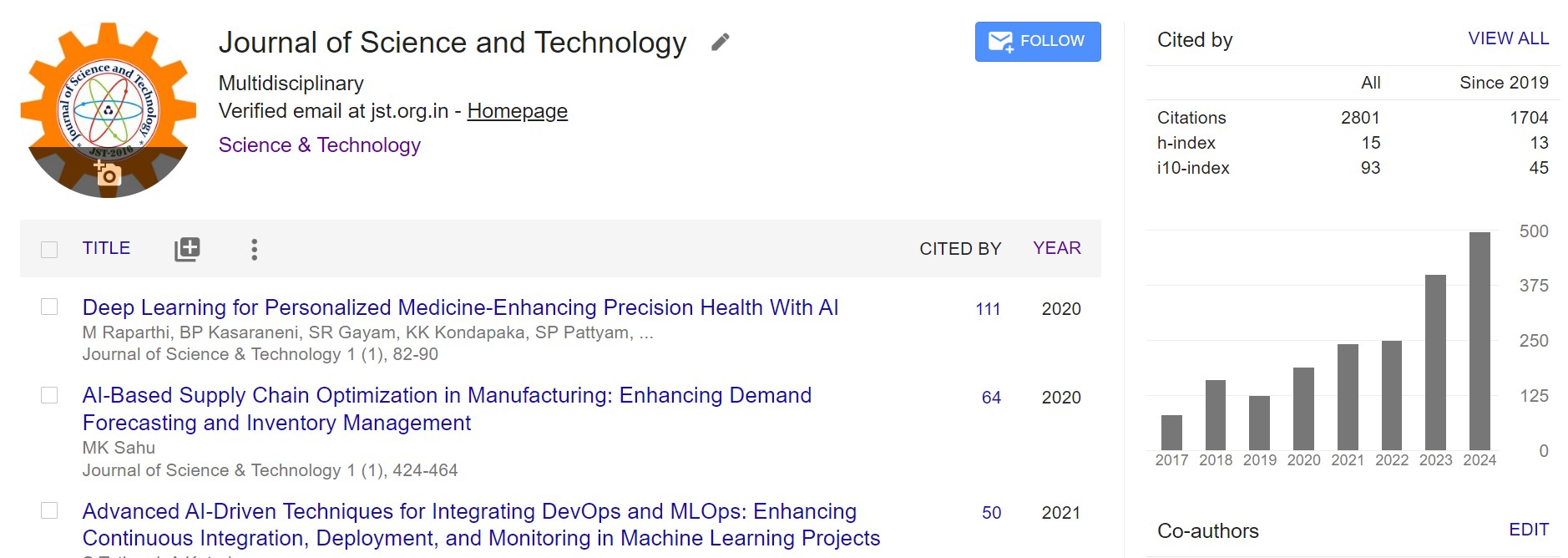

AbstractApproximate computing improves performance in error-resilient applications like image and video processing. Multipliers are part of its computing unit, which frequently requires a large number of resources. This study compares an approximation (8; 2) compressor to other known models in terms of quality, power consumption, delay, and circuit area. The proposed approximation compressor is implemented in 8 × 8 and 16 × 16 multipliers. To demonstrate the quality of the suggested compressor, an 8 × 8 approximation multiplier was utilized to multiply two images in MATLAB tools. Qualitative measures such as SSIM and PSNR were examined and acceptable results were obtained. The suggested 8 × 8 multiplier circuit produces an acceptable error rate, as indicated by the MED and NED accuracy criteria. Finally, we used a Synopsys Design Compiler to synthesize the proposed approximation compressor and multiplier designs. The suggested 16 × 16 multiplier improves latency, area, and power delay products by 5%, 17%, and 8%, respectively, compared to similar current approximate multipliers.