AN STRATEGY OF POWER AND AREA COMPETENT APPROXIMATE MULTIPLIERS

DOI:

https://doi.org/10.46243/jst.2023.v8.i01.pp06-18Keywords:

Algorithmic Noise Tolerant (ANT), Fixed-Width Multiplier, Reduced-Precision Replica (RPR), Voltage Over Scaling (VOS), Error Tolerant Adder(ETA), Main Digital Signal Processing(MDSP)Abstract

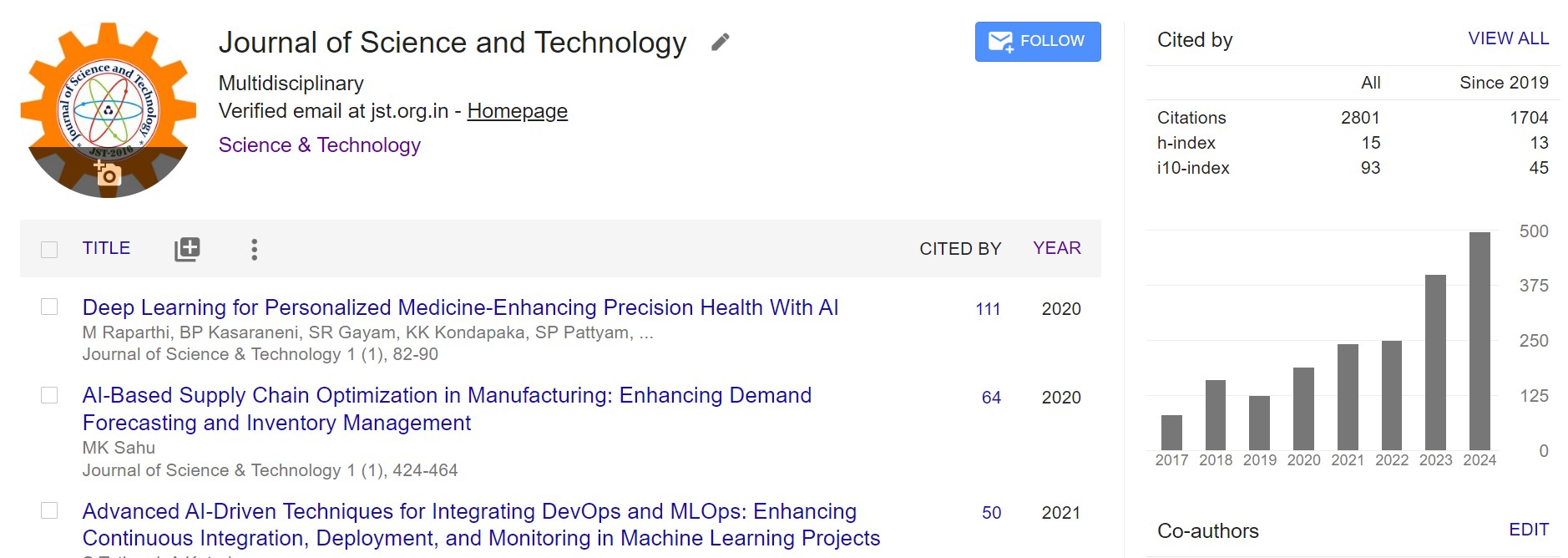

In this paper, the area of efficiency multiplier put a sign suggests a fixed width through a replica redundancy through adoption My tolerance for noise (ANT) architecture with a multiplier of fixed width to build a redundancy version precision cutting Masa (RPR). ANT proposed architecture can meet the demand for high precision, low power consumption, and region Efficiency. RPR fixed-width design with error compensation through the circles of the possibilities and statistical analysis. use the When a partial product of the correct input vectors and vectors fixed in the palace and put in place to reduce truncation errors, hardware Failure holding circuit can be simplified compensation. The multiplier ANT 16 × 16 bits, the circuit area in our RPR fixed width It may be less, energy consumption in the design of ants can be saved as compared with the ANT state of the art design.